Design of an Modular, Arbitrary word length RISC machine

Written 2009-04-07

Tags:Turing completeness Hardware Cellular Automata Design

I've always been impressed with the simplicity of the OISC ( one instruction set computer). One day, I had an interesting idea-Why not build it? In about six hours I had finished my first design on a whiteboard.

Now, the 7400 logic series contains a lot of 4-bit chips(registers, a counter I could use for a program counter, tri-state buffers, multiplexers, and full adders). A four bit OISC machine with direct addressing has only 16 words. Keep in mind that an instruction is 3 words. So a 4-bit oisc could only hold 5 instructions, with a 4-bit bank for data. So I set out to design an 8-bit machine.

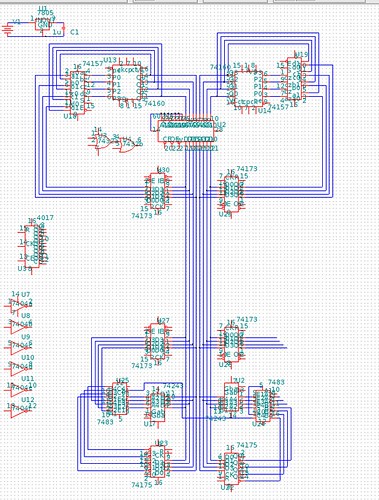

The first step in designing the 8bit machine was implementing effectively 8bit components out of 4bit parts. Almost all the necessary constructs are simply 2x4bit constructs. Here's an image of that first machine, partially implemented in oregano.

Did you notice the symmetry? You can implement an 8bit component with 2 4bit components and some control glue. Sadly, I had forgotten one very important step in the OISC architecture, and so my design was worthless-or so I thought. My roommate Ryan (of irontaco.com fame) showed me that what I had designed was still an cellular automata simulator. It was pretty cool, and I'll upload the schematics someday. However, it still wasn't a turing complete machine, so I set out to design it again.